### 論文の内容の要旨

# 論文題目:表面活性化常温接合(SAB)法を用いた Cu-Cu 超多端子バンプレス接続構造の開発

氏名:重藤 暁津

本論文は、表面活性化常温接合法(surface activated bonding, SAB)による Cu-Cu 間直接接合を超微細・低プロファイル Cu 電極の接続に応用することで、従来の配線接続技術では不可能であった  $10\mu m$  以下の超微細ピッチ・超多端子バンプレス接続を実現したものである。

## 1. 緒言

現在、システム LSI への異種信号混載・小型化の要求はますます加速している。それに答えるため、将来的にシステムデザインは個別モジュールのパッケージング (packaging)によるシステム構築に移行すると考えられている。このようなシステムを実現するために不可欠なのが高速信号伝送であり、そのためにはオフチップでの配線接続ピッチがチップ上層配線のそれと同等にまで微細化されなければならない。すなわち、10μm 以下のレベルの接続技術が開発されなければならない。しかしながら、バンプ状電極に段階的な加熱を印加する従来の接合方法では、熱膨張の不一致により接合界面に発生する歪みをバンプの変形で吸収することが困難なため、このような微細ピッチを達成することはできない。これに対する根本的な解として考えられるのが薄厚チップ・ウエハの接合によりシステム全体に可撓性をもたせることであるが、このような構造を得るためにはバンプ状電極を介さず、電極表面と絶縁体表面が同時に接触する接合構造が不可欠である。

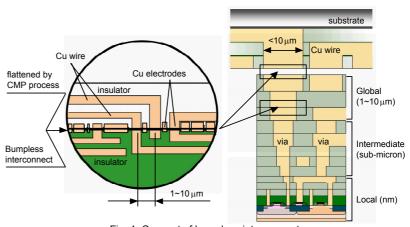

この観点から、本研究ではバンプを介さない接合構造としてバンプレス接合(bumpless interconnect)を提案した。その概念をFig. 1に示す。バンプレス接合においては、低抵抗のCu配線表のしては接または薄膜状の介して直接接続される。電極を介して直接接続される。電極表面とにおいる。にはに接触する。バン

Fig. 1. Concent of humpless interconnect

プレス接合構造の採用によってオフチップ-オンチップ間でスムーズな信号伝送が可能 になると期待される。

$10\mu m$  以下の超微細ピッチバンプレス接合の実現に不可欠なのが Cu 電極間の $\pm 1\mu m$  レベルの位置決め精度である。従って、加熱を用いる従来手法を適用することは不可能で、接合プロセスの低温下が求められる。また、接続部での RC 遅延を抑制するためには電極間が直接接続されることが望ましい。本研究で用いた表面活性化常温接合法は、高真空雰囲気中での Ar ビーム衝撃により表面の不活性層を除去することで活性面を創製し、接合を得るため加熱が必要ない。ただし、この接合法では試料は常温で接触するため、薄膜状の試料ではあらかじめ表面の平坦化を行う必要がある。よって、CMP (chemical mechanical polishing) プロセスなどによる Cu 表面の平坦化を行う。しかし、CMP プロセス後の Cu 表面状態は単結晶標準試料のそれとは大きく異なるため、CMP で平坦化された Cu 薄膜(CMP-Cu)の直接接合を得るためには、その表面の挙動を解析して接合条件を最適化しなければならない。その他にも、 $\pm 1\mu m$  レベルの精度を有する表面活性化法を用いた接続プロセスの開発も必要である。

以上のことから、本研究では表面活性化法による Cu 超微細バンプレス接合の実現を目的として、その主要な要素技術である CMP-Cu 薄膜常温直接接合の実現・表面活性化法を用いた高精度接合プロセスの開発・微細 Cu バンプレス電極形成プロセスの開発を行った。また、バンプレス接続構造の応用性を検討するため、バンプレス電極構造を有する実デバイスを試作し、動作検証を行った。

#### 2. 表面活性化常温接合法による CMP-Cu 薄膜直接接合の実現

表面活性化接合法において、接合性に影響する重要な因 子は表面の形状と清浄度である。まず、表面形状につい ては、従来から Hertz の弾性接触理論に基づく予測が行 われてきた。これは、表面間の凝着エネルギーが表面の 変形に要する弾性エネルギーより大きければ密着が進 行するというもので、表面を正弦は形状とみなした時の 波長と振幅をパラメータに用いている。本研究では、正 弦波形状ではない一般のCu表面の形状を評価するため、 機械的に実測可能な表面の平均曲率と平均粗さをパラ メータに用い、過去の研究例から全面的な接合を達成す るための形状条件の目安を平均曲率 10<sup>6</sup>m<sup>-1</sup>程度の Cu 薄 膜表面に対して平均粗さ約 2nm 以下と算出した。この平 坦度は保護性酸化被膜形成などの表面処理によって酸 化の進行を抑制することで長時間維持されることを確 認した。また、表面処理を行った試料に対し、XPS(x-ray photoelectron spectroscope)を用いた深さ方向分析から、 Cu清浄面を得るための必要エッチング量が15nmである ことが判明した。次に、表面の清浄度に関しては、上記 の活性化条件の下で得られた清浄表面間の接合性を真

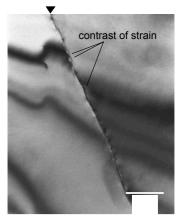

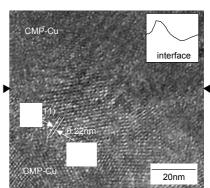

Fig. 2. TEM images of the interface between CMP-Cu films

空雰囲気に対する露出量 $(Pa \cdot s)$ をパラメータとして評価した。その結果、全面的な接合を得るための限界露出量が約 $0.2Pa \cdot s$ であることが明らかになった。その後、活性表面上に生成する酸化膜厚の成長速度の近似式から、上記の限界露出量下で生成する酸化物層厚は約2nmであると算出された。この値はCu表面で連続的な酸化被膜が形成したときの厚さ約3nmほぼ合致するので、連続的皮膜形成が接合性の可否を決定する要因である可能性が高いと考えられる。

得られた条件の下で CMP-Cu の直接接合を実現した。その界面の構造を TEM 観察した結果を Fig. 2 に示す。接合界面では、微小突起が変形することで表面間が密着し、 Cu-Cu 原子間の接合が達成されている。Ar 原子ビーム照射によるダメージ層や中間層が 観察されず、また、界面近傍の格子像に大きな変化がないことから、ビーム照射の影響は小さいと考えられる。さらに、界面に見られた歪みのコントラストは真空中 200℃程度の加熱によって縮小し、なだらかになったことから、加熱により歪み近辺の応力が緩和したと推測される。逆に考えると、常温接合界面は非平衡な状態にあり、その安定化のために接合後も強度や構造などに経時変化が発生する可能性を示唆している。

## 3. 表面活性化法を用いた超微細 Cu 電極のバンプレス接合の実現

表面活性化法を用いた高精度接続プロセスとして、高真空中で±1µmのアライメント精度を有する SAB フリップチップボンダを開発した。この装置は、高真空中での試料ハンドリング動作を可能にするためバネ式のチャックを備えたボンディングヘッドを有する。また、平坦な試料間の接続を可能にするため、ボンディングヘッドが揺動して互いの表面に倣う機構を付与した。超微細 Cuバンプレス電極の製作には、ダマシン手法と RIE(reactive ion etching)プロセスを併用する方法を開発した。これは、Cu

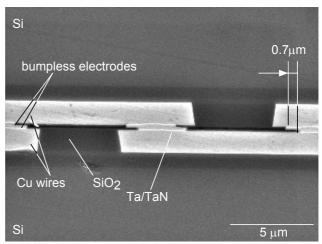

Fig. 3. Cross sectional view of bonded bumpless electrodes

と絶縁体が混在する表面を平坦化するに際して、絶縁体表面を優先的に研磨するためである。このプロセスを用い、 $3\mu m$  径電極を絶縁体表面からの高さ 60nm 以下・高さばらつき 2nm 以下の平坦さで 100,000 ピン・ $10\mu m$  ピッチの高密度で一括形成した。

これらを用いて超微細 Cu バンプレス電極を実現した。(Fig. 3.)100,000 全ピンが電気的に接続され、その界面でのは  $1m\Omega$ 以下の低い接触抵抗値が得られた。また、150  $^{\circ}$   $^{\circ}$  1000 時間の加熱加速試験において、接触抵抗の増加率は測定誤差範囲内の 5%以内であった。

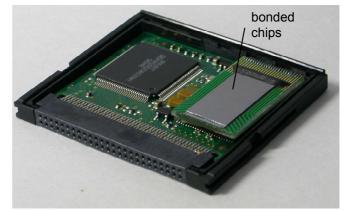

### 4. バンプレス接合の実デバイスへの応用性

バンプレス電極を有する 0.1mm 厚の薄型コンパクトフラッシュメモリチップを試作した。 0.1mm 厚試料は別の Si チップに貼り付けた状態で搬送され、この状態でチップの上部配線層に Cu ポストを形成し、ポリイミド絶縁層を塗布することでバンプレス構造を形成した。その後 CMP と酸素プラズマ照射によるCu 電極面の平坦化を行い、SAB フリップチップボンダで接合した。接

Fig. 4. Whole image of assembled bumpless CF memory chip.

合後、貼り付けた Si チップを剥離することで薄厚メモリチップを得た。これを市販の CF 基板から 128MB チップを除去し、その部分にワイヤボンディングで接続し、PC 装着によってその動作を検証した。その結果、100MB のデータの I/O がスムーズに行われ、接合が良好に進行したことが示された。

### 5. 結論

本研究では、表面活性化常温接合法による Cu-Cu 接合条件を明確にすることで、CMP プロセスで平坦化された Cu 薄膜(CMP-Cu)の常温直接接合を達成した。さらに、これを超微細・超低プロファイル電極の接続に適用し、 $3\mu m$  径・ $10\mu m$  ピッチ電極 100,000 ピンの超高密度バンプレス接続を実現した。また、実デバイスに Cu バンプレス接続構造を適用したところ良好に動作した。以上に関して、次のような知見を得た。

- 1. CMP-Cu 表面間の全面的な接触を得るための条件は平均曲率 K と平均粗さ Ra を用いて記述することができ、 $1x10^6m^{-1}$ 程度の平均曲率を持つ Cu 薄膜に対し、接合を得られる平均粗さ Ra は約 2nm 以下と算出された。保護性酸化皮膜の形成などの表面処理により、この平坦度は長時間維持することができる

- 2. 全面的な接合を達成するための限界露出量が約 0.2Pa・s 以下であることを明らかにした。酸化物層厚は成長速度の近似式から約 2nm と算出され、この値は連続的な酸化物層が形成厚さ約 3nm とほぼ一致するので、接合性の可否を決定する要因は連続的被膜の形成である可能性が高いと考えられる。

- 3. CMP-Cu 薄膜試料の界面においては、微細な表面変形などによって表面が整合することで密着が進行し、Cu 原子どうしの接合が達成された。また、表面の変形によって生じた歪みは加熱に伴い緩和し、界面は安定する傾向にあることが判明した。

- 4. バンプレス電極の接合界面では 1mΩ以下の低接触抵抗値が実現された。また、加熱加速に伴う抵抗増加率はわずかで信頼性は高いと考えられる。

- 5. バンプレス電極を有する薄型メモリチップは良好に動作し、高い応用可能性を示した。