## 論文の内容の要旨

## 論文題目 シュタルクアトムチップの設計・製作に関する研究

## 氏 名 長藤 圭介

1970年代に原子のレーザー冷却が発明されて以来,冷却原子を用いた量子物理の基礎研究が盛んに行われてきた.中でもボーズ-アインシュタイン凝縮と呼ばれる巨視的凝縮体を実証した功績には、レーザー冷却技術と同様にノーベル物理学賞が与えられた.一方で,冷却原子を量子素子とした量子情報処理の研究が始まり,原子による量子コンピュータの実現に向けて,原子を固体基板上で操作する「アトムチップ」の開発研究が行われている.原子を基板上で操作するメリットは,量子効果が発現する遷移波長程度の原子の位置制御の可能性があること,微細化に伴い装置全体の小型化が可能であることが挙げられる.

アトムチップの主流はイオントラップと磁場トラップである. イオントラップは電荷をもつ原子と4重極電極とのクーロン力によりトラップする. 磁場トラップはスピンをもつ中性原子と,チップ上にパターニングされたワイヤがつくる磁場との相互作用により基板上空でトラップするものである. いずれのアトムチップも,基板表面のつくる外乱に敏感で集積化に限界があるとされる. これに対し,香取らはスピンを持たない原子のトラップ方法として,ポテンシャルが電場の2乗に比例するシュタルクシフトを制御場としたシュタルクアトムチップを提案した. 電極がつくる不均一電場を一定の周波数で切り換えることで,電極中心に動的にトラップするというものである.

本研究では、このシュタルクトラップを実証するためのシュタルクアトムチップの試作を行った。また、微細化・集積化を目指したアトムチップの構造および加工設計を行った。このチップの形態の初期のものとして、トラップサイトを1次元的に並べたラティスアトムチップを選び、その設計・加工方法を確立した。

シュタルクトラップ電極の基本形は、4つの電極が対称に配置されたものである.それぞれ+V/-V/GND/GNDに電圧を印加すると、その中心付近に鞍形のポテンシャル(シュタルクポテンシャル: $U=-(1/2)\alpha|\vec{E}|^2$ , $\alpha$ : 分極率, $\vec{E}$ : 電場)が形成される.これをある周波数で切り換えることで、中性原子を中心付近に動的にトラップする.分極率が正の場合z方向は調和ポテンシャルであるため、xy平面のポテンシャル切り換えは影響しない.イオントラップはイオンと電場とのクーロン力を、磁場トラップはスピンと磁場とのゼーマンシフトを用いている.それぞれ電場、磁場との1次の相互作用であるのに対してシュタルクトラップは電場と2次の相互作用であるため制御性は劣るが、外場からのノイズを受けにくい.よって電極微細化に伴って有利である可能性がある.

シュタルクトラップを実証するために、「 $S_0$ 状態の冷却  $^{88}$ Sr原子を用いる.冷却原子のシュタルクトラップを行うためにはレーザー冷却・電極への輸送が大きな課題となる. (1)電極上空でMirror Magneto-Optical-Trap (Mirror-MOT) で冷却,(2)対向レーザーにより Far-off resonance lattice trap (FORT) 輸送,(3)シュタルクトラップ,(4)再び FORTによりチップから引き戻し原子の有無を確認する.これらの手順から,シュタルクトラップチップの要求機能(FR: Functional Requirement)を抽出する.FR1: Mirror-MOTのための反射率,FR2: FORTのための電極中心透過率,FR3: 電場をつくるための金属が薄いこと(~100 nm,熱ノイズ減少のため),FR4: 電極加工精度,の4つとした.MOT→FORTが可能なシュタルク電極幅を50 μmとした.また電極厚さは,適度なトラップ周波数特性をもつ100 μmとした.これらを満たす設計解として,(1) Focused ion beam(FIB)により厚さ100 μmのガラス基板中心に十字貫通加工する,(2) 基板を斜めにしながらAgスパッタにより上面および側面にミラーおよび電極を作製する,(3) FIBにより4電極間を絶縁しシュタルク電極を作製する,(4) FIBは加工レートが低いため,広範囲( $\Box$ 0.5 mmの外側)の電極絶縁は,紫外線レーザー加工を用いてAg薄膜をアブレーションすることで行う,(5) ARコーティングされたガラス基板に貼り付ける.このチップを真空ポートに超真空対応エポキシを用いて貼り付け,電極を取り出す.

実際に加工した電極は、加工側の幅が $50~\mu$ mに、手前の幅が $44~\mu$ mに仕上がっていた。これはFIBで貫通十字を加工する際に、奥行き方向にイオンビームのパワー密度が落ち、テーパになったと考えられる。この加工誤差を検証するためにFEMによる電場計算およびRunge-Kutta法を用いてトラップ効率の検証を行った。テーパになると、理想的な垂直電極に比べて、トラップ可能周波数域が高くなるが、下電極幅 $40~\mu$ mまで、ほとんど効率が変わらないことがわかった。ここでは省略するが、実際の実験による周波数特性は、このテーパの計算結果に良く合っていた。

このアトムチップを用いて香取研究室において実際に実験を行った. 原子にプローブ 光を当てた時点で、原子は加熱されるため、このイメージングは破壊測定である. この 実験から、理論温度 $7\,\mu K$ のSr原子の最大トラップ数(印加電圧: $\pm 200\,V$ 、駆動周波数: 6.4 kHz)が約100、ライフタイムが約 $80\,ms$ であることが分かった.

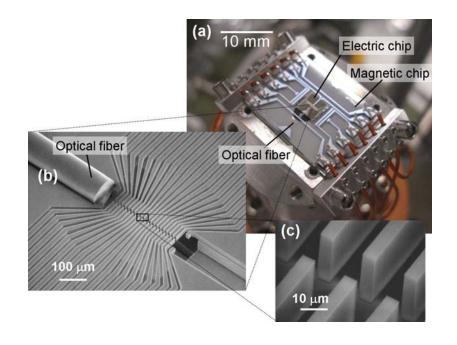

次の段階として、トラップサイトを1次元にアレイ化する「シュタルクラティスアト ムチップ」の設計・製作を行った. 隣同士の電極は、間の電極を兼ねて、互い違いに電 圧をかける. 電極間隔と電極幅を足したものが、トラップサイトのピッチとなる. 前述 した50 μm間隔のトラップでは、電圧は±200 Vと、比較的高電圧であった。今回実証す るトラップでは、微細化し低電圧駆動を目指したサイズとする. そこで電極間隔を10 μm, 電極高さ20 μm, 駆動電圧は±32 Vでトラップチップと同様のトラップ深さのポテンシャ ルを生成する. 電極幅は5 μmとし、トラップピッチは15 μmとなる. 電極間隔が10 μm あるいはそれ以下になると、50 μmチップで用いたFORTレーザーを電極幅以下に絞る 必要があり、結果Rayleigh長がMOT中心に届かなくなり使えない. そこで、Sr原子にス ピンを持たせ( ${}^{3}P_{2}$ ) 磁場により輸送する方法を用いる. (1) チップ上空でMOTを行う, (2) MOTにより集めた原子をレーザートラップ (レーザーピンセット) によりシュタル ク電極上空へ輸送する,(3)チャンバ外のバイアスコイルによる磁場とチップ上のワイ ヤによる磁場によりシュタルクチップへ輸送, (4) 電場トラップ, (5) プローブ光を照 射し磁場チップの裏から高NAで原子を観察する. ここで、50 μmチップのようにミラー の機能を設けると電極設計の制約条件が増えるため、ここではチップの斜め裏から MOT光を導入する手法を選んだ. これらの手法からチップの要求機能は, FR1: シュタ ルク電極の裏を光学的にフリーにする、FR2: チップ上空20 mmの位置にMOTが可能な チップサイズ, FR3: シュタルク電極に安定にプローブ光を照射できること, FR4: 電極 加工精度, とした. 最も困難な要求機能はFR1である. シュタルク電極の真下に設置す る磁場チップのワイヤをU形にする. 裏面からの光学観察および電流値10 A程度を実現 するために,光学研磨されたサファイア (熱伝導率:~40 W/m·K) 基板を用いる. ま た,シュタルク電極の真下を光学的にフリーにするため,今回はSilicon-on-Insulator (SOI) 基板を用いたMEMSプロセスを採用する. FR2を満たすためにチップ幅は18 mmとした. FR3を満たすため、シュタルク電極の横に光ファイバを設置し、近接したファイバ先端 から $^{1}S_{0}$ - $^{1}P_{1}$ 遷移波長460 nmをプローブさせる方法を考えた. そこで電極中心に真っ直ぐ プローブできるように、ファイバガイドをシュタルク電極作製プロセス中に同時作製す

シュタルク電極のプロセスフローを示す.磁場輸送設計において,磁場チップに流せる電流値を10 A以下に設定したため,ワイヤからシュタルクトラップ電極までの高さを200  $\mu$ mとするために,SOIのハンドリング層を160  $\mu$ mになるようにバックポリッシュしている.光ファイバはクラッド径125  $\mu$ mのものを用いるため,シュタルク電極(デバイス層: 20  $\mu$ m)の中心に光ファイバの中心が来るように,ハンドリング層を52  $\mu$ m掘る.そのため,エッチング開始前に二重のマスクを作製しておく必要がある.なお,ハンドリング層のバックエッチングを行うため,裏面にAlマスクを裏面アライメントによるフォトリソにより作製しておく.シュタルク電極,ファイバガイド,バックエッチングはいずれもMEMSプロセスでは一般的なSi垂直深堀エッチング(Deep-RIE: Deep Reactive Ion Etching,or Bosch process)を用いた.磁場チップは,サファイア基板にAlをスパッタにより20  $\mu$ m成膜,フォトレジストをマスクとしてウェットエッチングによりAlワイヤをパターニングした.この磁場チップにシュタルク電極をTorr sealを用いて貼りつけ,真空に導入する長さ(10  $\mu$ m程度)分の被覆を剥き先端を研磨した光ファイバをマイクロマニピュレータによってファイバガイドに取り付ける.

対称4電極のうち1電極が理想的な位置からずれた場合のトラップ効率の試算結果を行った.電極間隔に対して5%ずれるとトラップ効率が約半分になる.また10%遠ざか

る方向にずれるとほとんどトラップできなくなる.シュタルクトラップチップでは50  $\mu$ mの電極間隔に対して1  $\mu$ m以内の誤差に入っていたため,理想的な寸法の電極によるトラップ効率を保っていたと言える.シュタルクラティスアトムチップでは電極間隔10  $\mu$ mに対して500 nm以内の誤差が目安となる.電極先端が丸まってしまった場合,電極間隔10  $\mu$ mに対して角のRが2.5  $\mu$ mになるまで効率が下がらないことが分かった.ラティス電極によるトラップでは,トラップサイトから見て電極の表面すなわち等電位面が非対称になる.そこで,設計した電極形状でトラップ可能か,計算により検証した.電極幅5  $\mu$ mを固定し,横方向(アレイ方向)の幅を変化させたところ,トラップ効率は幅10.5  $\mu$ m付近で最大値をとる.横方向に電極幅が狭いことでその面がつくる電場が弱くなるためだと考えられる.

次に、微細電極の試作を行った. Deep-RIE後の側面の平坦化に、熱酸化および酸化膜エッチングを用いた. ピッチ450 nmのラティスチップをD-RIEにより基本構造を作製した後、1気圧 $O_2$ 下1000 $\square$ , 30 minで酸化、BHFにより酸化膜エッチングを行った. SEM観察により側面のP-Vは約45 nmから10 nm以下に平坦化できた.

シュタルクアトムチップのトラップ実証電極の設計および製作を行い,実際にトラップできることがわかった.次の段階として,微細電極トラップのためのラティスアトムチップの設計・製作を行った.また加工誤差を考慮して電極形状に対するトラップ効率の試算を行い,実現可能性を確かめた.また,SiのDeep-RIE後の熱酸化および酸化膜エッチングにより側面の平坦化を試み,側面のP-V10 nm程度の平坦側面をもつピッチ450 nmのラティスチップの試作を行った.

本研究の一部は、日本学術振興会特別研究員 (H18~H20) 研究奨励費により行った. レーザー冷却原子を用いた実験は東京大学物理工学専攻香取研究室にて行われた.シュタルクラティスチップのMEMSプロセスの一部は、東京大学大規模集積回路設計教育センター (VDEC) の装置を用いて行った.

- [1] K. Nagato, T. Ooi, T. Kishimoto, H. Hachisu, H. Katori, M. Nakao, "Design and prototyping of stark atom chip for electric trapping of laser-cooled atoms", Precision Eng. 30 (2006) 387.

- [2] T. Kishimoto, H. Hachisu, J. Fujiki, K. Nagato, M. Yasuda, H. Katori, "Electrodynamic trapping of spinless neutral atoms with an atom chip", Phys. Rev. Lett. 96 (2006) 123001.